DynamiX: A scalable charge cancellation high frame-rate architecture for hard X-ray

measurements

Presenter: Thomas Gardiner, Science and Technology Facilities Council, United Kingdom

Primary authors: GARDINER, Thomas (STFC Rutherford Appleton Laboratory); BELL, Stephen (STFC Rutherford Appleton

Laboratory)

Co-authors: WILSON, Matt (Science & Technology Facilities Council); NOBES, Joseph (STFC Rutherford Appleton

Laboratory); Mr LARKIN, Matt (STFC Rutherford Appleton Laboratory); Mr DAVIS, Adam (STFC Rutherford Appleton

Laboratory); Mr KNOWLES, Simon; Mr PRYDDERCH, Mark (STFC Rutherford Appleton Laboratory); VEALE, Matthew (STFC

Rutherford Appleton Laboratory); HART, Matt (STFC Rutherford Appleton Laboratory)

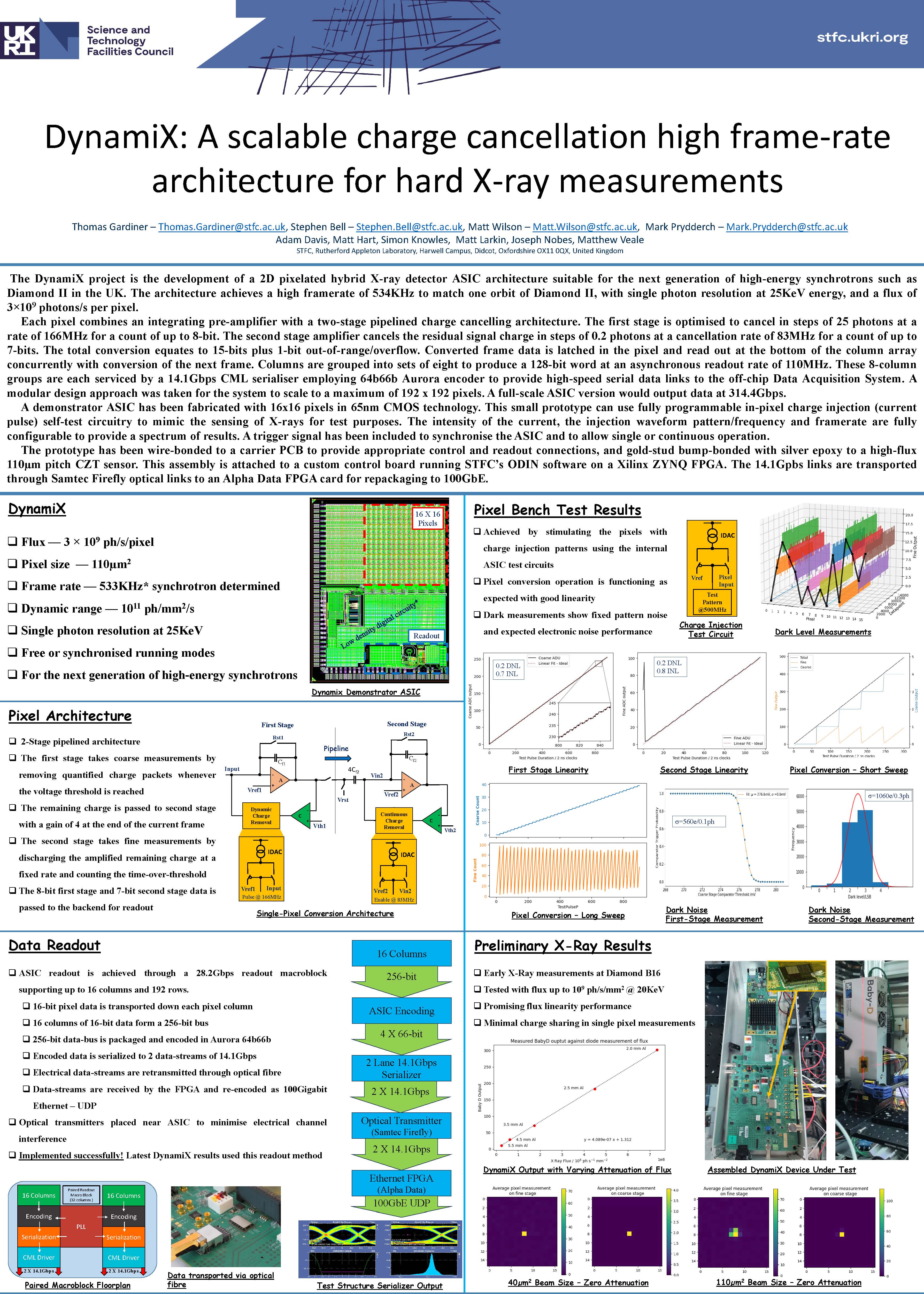

The DynamiX project is the development of a 2D pixelated hybrid X-ray detector ASIC architecture suitable for the next generation of

high-energy synchrotrons such as Diamond II in the UK. The architecture achieves a high framerate of 534KHz to match one orbit of

Diamond II, with single photon resolution at 25KeV energy, and a flux of 3×109 photons/s per pixel.

Each pixel combines an integrating pre-amplifier with a two-stage pipelined charge cancelling architecture. The first stage is optimised

to cancel in steps of 25 photons at a rate of 166MHz for a count of up to 8bit. The second stage amplifier cancels the residual signal

charge in steps of 0.2 photons at a cancellation rate of 83MHz for a count of up to 7-bits. The total conversion equates to 15-bits plus

1-bit out-of-range/overflow. Converted frame data is latched in the pixel and read out at the bottom of the column array concurrently

with conversion of the next frame. Columns are grouped into sets of eight to produce a 128-bit word at an asynchronous readout rate

of 110MHz. These 8-column groups are each serviced by a 14.1Gbps CML serialiser employing 64b66b Aurora encoder to provide

high-speed serial data links to the off-chip Data Acquisition System. A modular design approach was taken for the system to scale to a

maximum of 192 x 192 pixels. A full-scale ASIC version would output data at 314.4Gbps.

A demonstrator ASIC has been fabricated with 16x16 pixels in 65nm CMOS technology. This small prototype can use fully programmable

in-pixel charge injection (current pulse) self-test circuitry to mimic the sensing of X-rays for test purposes. The intensity of the current,

the injection waveform pattern/frequency and framerate are fully configurable to provide a spectrum of results. A trigger signal has

been included to synchronise the ASIC and to allow single or continuous operation.

The prototype has been wire-bonded to a carrier PCB to provide appropriate control and readout connections, and gold-stud bumpbonded with silver epoxy to a high-flux 110µm pitch CZT sensor. This assembly is attached to a custom control board running STFC’s

ODIN software on a Xilinx ZYNQ FPGA. The 14.1Gpbs links are transported through Samtec Firefly optical links to an Alpha Data

FPGA card for repackaging to 100GbE.

Electrical and X-ray tests are currently in-progress and results will be presented.

Poster

Return to SRI2024 event page.